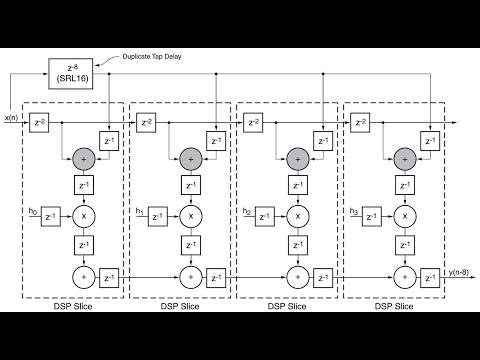

#FPGA #DSP #Xilinx #FIR Description Implementing an efficient parallel FIR filter in VHDL. The implementation is aimed at the Xilinx 7 families. References [1]Xilinx, “UG479 7 Series DSP48E1 Slice” [2] Udo Zӧlzer, ” Digital systems” in DAFX: Digital Audio Effects [3] , , , “8.4 Pipelining DSP System ” in FPGA-based Implementation of Signal Processing Systems [4] Richard G. Lyons, “ Improving Traditional CIC Filters” in Understanding Digital Signal Processing [5]Xilinx, “DSP48E1 Switching Characteristics ” in Zynq‐7000 SoC : DC and AC Switching Characteristics Sources Filter code: Coefficient translator:

- 30165Просмотров

- 4 года назадОпубликованоDimitar H. Marinov

FPGA and DSP ep. 1:Efficient parallel FIR filter implementation on FPGA

Похожее видео

Популярное

Preview Disney 2006 effects

flip the frog the goal rush

потерянній снайпер 2

губка боб бабуся

Molest

Потерянный снайпер 2

Красная гадюка 4часть

пупок женщины

jetix

Universal 1997 2012 effects

Грань провосудия 3

Плюсплюс

Robinhood sreeleela songs

سكس

ангелина

винни пух ну погоди

ну погоди 17-18 выпуск

Китай сериали

топтыжка

маленький шеф карусель

Boo boo song the milk maks

ПОТЕРЯННЫЙ СНАЙПЕР2

смешарики спорт

CPXV02 14

Cartoon network russian

flip the frog the goal rush

потерянній снайпер 2

губка боб бабуся

Molest

Потерянный снайпер 2

Красная гадюка 4часть

пупок женщины

jetix

Universal 1997 2012 effects

Грань провосудия 3

Плюсплюс

Robinhood sreeleela songs

سكس

ангелина

винни пух ну погоди

ну погоди 17-18 выпуск

Китай сериали

топтыжка

маленький шеф карусель

Boo boo song the milk maks

ПОТЕРЯННЫЙ СНАЙПЕР2

смешарики спорт

CPXV02 14

Cartoon network russian

Новини