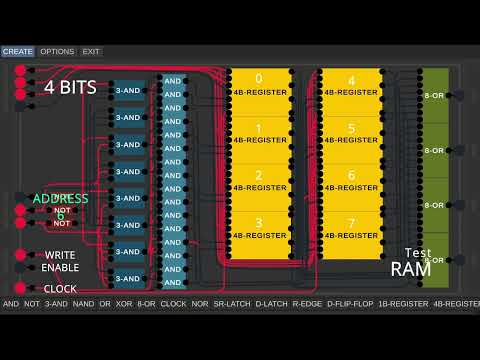

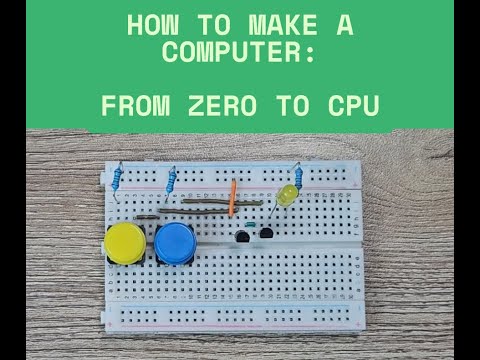

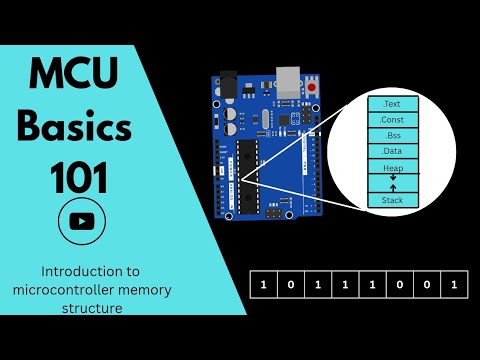

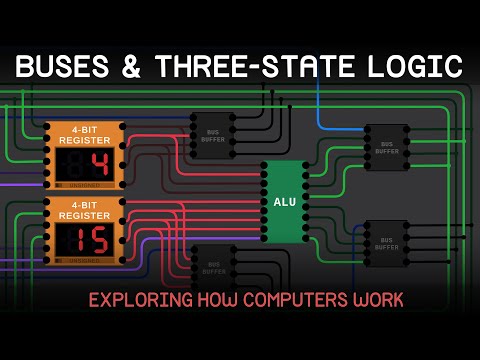

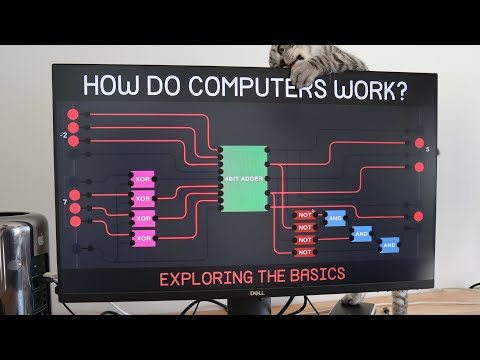

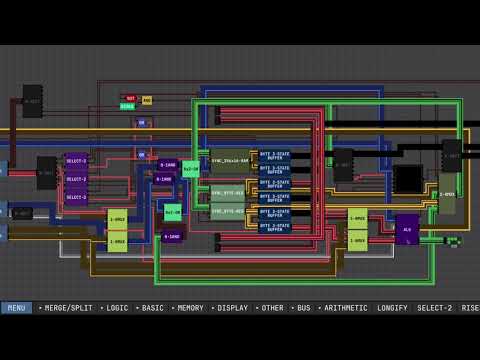

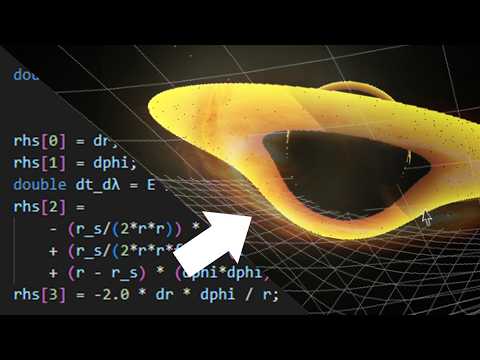

Let’s try building a whopping 256 bytes of random access memory (inside a digital logic simulation). This is part 5 of my journey to explore the basics of how computer’s work. If you’d like to watch the other episodes, you can find the full playlist here: The simulation program is in a slightly rough and unstable state as I’m developing it as I go, but if you’d like to try it out, the latest version (and source code) is available over here: If you’d like to support me in creating more videos, consider becoming a patron of the channel: This series was largely inspired by the 8-bit breadboard computer series by @BenEater (so be sure to check that out if you haven’t already)! Image and music credits: Chapters: 00:00 Intro and a New Simulation 01:50 A Grid of Latches 03:12 Decoder 04:42 1-Bit Memory Cell 06:42 Rambling about Dynamic and Static Memory 08:46 16 Bits of Memory 11:41 Surprise Inspection 12:16 256 Bits of Memory 14:28 Asynchronous RAM 18:02 A Brief Note Concerning Caches 19:00 Synchronous RAM 22:28 Equality Chip 23:28 The Final Test 24:37 A Trip Down Memory Lane

- 404625Просмотров

- 8 месяцев назадОпубликованоSebastian Lague

Simulating 256 Bytes of RAM

Похожее видео

Популярное

ШАРЛОТТА ЗЕМЛЯНИКА

Красная гадюка 6

Безжалостный гений

оазис

Sex

Autoroute mdiq tetouan

ангелина

Noddy

Красная гадюка 5

потерянный снайпер 6 серия

the 70s show

УМ. БЕЛЫЙ ДЕЛЬФИН

губка боб хорошие соседи

спагетти макароны

Красная гадюка 17-20 серии

смешарики

лалапупси реклама

poterianij snaiper 3 seria

Dia de piscina com as meninas

дисней добрлас

дорожная азбука

Красна я гадюка 4

Красная гадюка 6

Безжалостный гений

оазис

Sex

Autoroute mdiq tetouan

ангелина

Noddy

Красная гадюка 5

потерянный снайпер 6 серия

the 70s show

УМ. БЕЛЫЙ ДЕЛЬФИН

губка боб хорошие соседи

спагетти макароны

Красная гадюка 17-20 серии

смешарики

лалапупси реклама

poterianij snaiper 3 seria

Dia de piscina com as meninas

дисней добрлас

дорожная азбука

Красна я гадюка 4

Новини