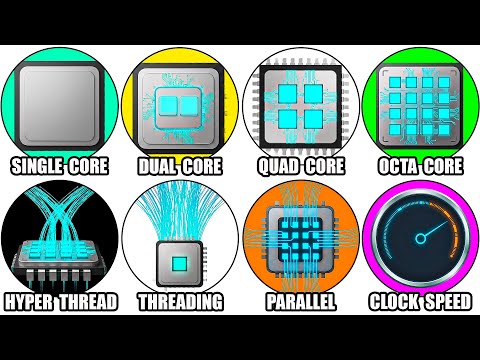

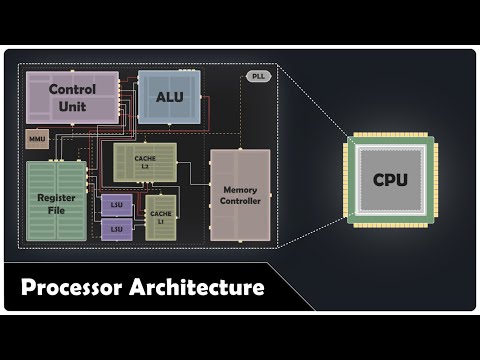

Every CPU Cache Level Explained in Detail Why do fast CPUs still wait on memory? Cache. In this video, we explain what CPU cache is and how L1, L2, L3 (and L4) work together to slash latency. Learn the differences between SRAM vs DRAM, instruction vs data cache, typical sizes/latencies, and how the cache hierarchy promotes data from L3 → L2 → L1. We also cover inclusive vs exclusive vs non-inclusive policies, associativity, spatial/temporal locality, and why some chips add off-die L4 (eDRAM/LLC). Perfect for PC builders, students, and anyone chasing real performance. #CPU #ComputerArchitecture #Cache #PCHardware #engineering SOME OF MY MOST POPULAR VIDEOS: Disclaimer: At Tech in a Teacup, we do our best to research, fact-check, and simplify complex tech topics into clear explanations. Still, technology evolves quickly, and occasional mistakes, mispronunciations, or oversights may happen. Our content is for educational purposes only and should not replace official documentation or professional advice. If you spot an error or have a correction, please share it kindly in the comments, we’re always learning and improving, video by video. Thanks for being part of this journey with us!

- 5245Просмотров

- 3 недели назадОпубликованоTech in a Teacup

Every CPU Cache Level Explained in Detail

Похожее видео

Популярное

Красная гадюка 4часть

Потерянный снайпер 6

Волчий берег11серии

mickey Valentine day party part 2

Classic caliou

Красная гадюка 2

Robinhood sreeleela

катя и эфир

Бурное расследование 2

чаггингтон реклама

Бурное безрассудство2

дисней добрлас игрушки

шопкинс реклама

незнайка за рулем

Городской снайпер 2 серия

Погода

ну погоди диск

Красная гадюка 7 серия

Потеряний снайпер 2часть

Preview 2 stars in the sky extended^4

Грань правосудия

Сериал я жив

Bridget Regan

Бурное безрассудство 2

ГРАНЬ ПРАВОСУДИЯ

Потерянный снайпер 6

Волчий берег11серии

mickey Valentine day party part 2

Classic caliou

Красная гадюка 2

Robinhood sreeleela

катя и эфир

Бурное расследование 2

чаггингтон реклама

Бурное безрассудство2

дисней добрлас игрушки

шопкинс реклама

незнайка за рулем

Городской снайпер 2 серия

Погода

ну погоди диск

Красная гадюка 7 серия

Потеряний снайпер 2часть

Preview 2 stars in the sky extended^4

Грань правосудия

Сериал я жив

Bridget Regan

Бурное безрассудство 2

ГРАНЬ ПРАВОСУДИЯ

Новини